An interface standard called PCIexpress, or PCIe for short, enables communication between your CPU and motherboard through several slots.

In the constantly changing field of PC technology, there is a growing discussion between PCIe 4.0 versus PCIe 5.0.

PCIe 4.0 has been a standard for motherboards and graphics cards, nevertheless, PCIe 5.0 is on the rise and promises major improvements.

The possibility of this update has already been alluded to by Intel and other significant players, particularly about CPUs, SSDs, and GPUs.

However, given that both models provide remarkable PCIe and Giga transfer bandwidth, how do they compare in real terms?

The main distinctions between PCIe 4.0 and PCIe 5.0 are examined here, along with how these developments will affect data-intensive applications and high-speed computing in the future.

Anyone hoping to fully utilize the capabilities of contemporary hardware solutions must comprehend these distinctions.

Learn More About: PCIe GEN6 Controller IP

What is PCIe?

High-speed component connections can be made via the PCIe (peripheral component interconnect express) interface standard.

There are multiple PCIe slots on every desktop PC motherboard that can be used to add RAID, Wi-Fi, GPU (also known as video or graphics), or SSD (solid-state drive) add-on cards.

The motherboard you purchase will determine the kinds of PCIe slots that are available on your computer.

There are various physical configurations of PCIe slots, including x1, x4, x8, x16, and x32.

The number that follows the x indicates how many lanes or channels that PCIe slot has for data transfer to and from the PCIe card.

One lane and one bit of data transfer per cycle are available in a PCIe x1 slot. Two lanes and two bits per second can be moved by a PCIe x2 slot.

According to Technavio, The PCI express market size is estimated to increase by USD 53.74 billion and grow at a CAGR of 28.22% between 2023 and 2028.

The growing demand for data centers and the corresponding building costs are driving significant growth in the PCI Express (PCIe) market.

What are the generations of PCIe?

There have been six PCIe generations released into the market thus far: PCIe 1.0, PCIe 2.0, PCIe 3.0, PCIe 4.0, PCIe 5.0, and PCIe 6.0.

PCI Express 1.0

With a per-lane data rate of 250 MB/s and a transfer rate of 2.5 giga transfers per second (GT/s), PCI-SIG released PCIe 1.0a in 2003.

Because the number of transfers includes the overhead bits, which do not increase throughput, the transfer rate is given in transfers per second rather than bits per second.

PCIe 1.x employs an 8b/10b encoding technique, which results in a 20% (= 2/10) overhead on the raw channel bandwidth.

Therefore, the phrase “transfer rate” in PCIe refers to the encoded bit rate; for example, 2.5 GT/s corresponds to 2.5 Gbit/s on the encoded serial link.

This is equivalent to 250 MB/s or 2.0 Gbit/s of pre-coded data, which is what PCIe refers to as throughput.

PCI Express 2.0

On January 15, 2007, PCI-SIG declared the PCI Express Base 2.0 specification to be available.

The PCIe 2.0 standard increases the per-lane throughput from 250 MB/s to 500 MB/s and doubles the transfer rate from PCIe 1.0 to 5 GT/s.

As a result, an aggregate throughput of up to 8 GB/s can be supported via a 16-lane PCIe connector (x16).

PCIe v1.x cards and PCIe 2.0 motherboard slots are completely backward compatible.

By utilizing PCI Express 1.1’s available bandwidth, PCIe 2.0 cards can also typically be used in a backward compatible manner with PCIe 1.x motherboards.

In general, motherboards or graphic cards made for v2.0 are compatible; v1.1 or v1.0a are not.

PCI Express 3.0

After several delays, revision 3.0 of the PCI Express 3.0 Base specification became available in November 2010.

PCI-SIG declared in August 2007 that PCI Express 3.0 would support both legacy PCI Express implementations and carry a bit rate of 8 Giga transfers per second (GT/s).

Additionally, it was revealed at the same time that Q2 2010 will be the final release date for the PCI Express 3.0 specification.

Several optimizations for improved signaling and data integrity were added to the PCI Express 3.0 specification, including clock data recovery, transmitter and receiver equalization, PLL enhancements, and channel improvements of topologies that are currently supported.

PCI Express 4.0

The preliminary PCI Express 4.0 announcement was made by PCI-SIG on November 29, 2011.

It doubles the bandwidth offered by PCI Express 3.0 to 31.5 GB/s in each direction for a 16-lane configuration at a bit rate of 16 GT/s while preserving backward and forward compatibility in terms of used mechanical interface and software support.

PCI Express 5.0

PCI-SIG released the PCI Express 5.0 preliminary specification in June 2017.

In a 16-lane arrangement, bandwidth was predicted to rise to 32 GT/s, producing 63 GB/s in each direction.

2019 was supposed to see the standardization of the draft spec.

In the beginning, 25.0 GT/s was also taken into account for technical viability.

PCI Express 6.0

The PCI-SIG announced the creation of the PCI Express 6.0 specification on June 18, 2019. Learn More About: PCIe GEN6 Controller IP

With a target deployment date of 2021, bandwidth is anticipated to expand to 64 GT/s, producing 128 GB/s in each direction in a 16-lane setup.

Non-return-to-zero (NRZ) modulation is replaced by 4-level pulse amplitude modulation (PAM-4) with a low-latency forward error correction (FEC) in the new standard.

In contrast to earlier PCI Express versions, PAM-4 is utilized as the line code to ensure that two bits are communicated every transfer, and forward error correction is employed to boost data integrity. In an x16 setup, up to 121 GB/s in each direction is achievable with a data transfer rate of 64 GT/s (raw bit rate).

After going over the foundations of PCIe and its generational improvements, we now turn our attention to the main topic of our discussion, a thorough comparison of PCIe 5.0 versus PCIe 4.0.

Understanding of PCIe 4.0

PCIe 4.0 Overview

The fourth generation of Peripheral Component Interconnect Express (PCIe) extension bus specifications is called PCIe 4.0, or PCIe Gen 4. The PCI Special Interest Group (PCI-SIG) is responsible for developing, publishing, and maintaining PCIe standards.

In 2011, PCI-SIG declared that PCIe 4.0 was under development, and in 2017, PCIe 4.0, Version 1.0, was formally published.

High-performance computer makers are racing to implement PCIe 4.0, the fastest PCIe generation currently on the market, for their clients, as it offers 16 giga transfers per second (GT/s).

This increase in transfer rate doubles the individual bandwidths that users can expect from the x1, x2, x4, x8, or x16 PCIe slots on their motherboards.

What does PCIe 4.0 do?

Like earlier PCIe versions, PCIe 4.0 allows high-speed data transfer from extension cards such as RAID cards, graphics cards, and NVMe SSDs via interacting with the computer’s motherboard.

A communications interface and driver called NVMe (Non-Volatile Memory Express) makes use of PCIe’s higher bandwidth.

Its goal is to make a wide range of client and enterprise systems compatible while simultaneously improving performance and efficiency.

NVMe was created specifically for SSDs and uses high-speed PCIe connections to interact without form factor constraints between the storage interface and the CPU of the system.

Regarding cards, this process is made possible by inserting these expansion cards into PCIe slots on the motherboard.

PCIe slots, which may or may not be installed on a PCIe 4.0 motherboard, are used to accommodate PCIe 4.0 expansion cards, such as this $89 ASUS Hyper M.2 x16 PCIe 4.0 x16 card, which is utilized for high-performance PCIe 4.0 NVMe SSDs.

PCIe 3.0’s total throughput is 16Gbps while PCIe 4.0 has double the throughput of PCIe 3.0. It offers up to 16 lanes and can transfer data at up to 32,000MB/s while SATA III transfers only up to 600MB/s.

As from the PC World review, A single Gigabyte Aorus M.2 PCIe 4.0 SSD achieves read speeds of 5GBps and write speeds of 4.3GBps. This represents approximately a 35% increase in sequential performance compared to some of the faster M.2 PCIe 3.0 SSDs available.

Gigabyte used a PCIe 4.0 add-in card to hold four 2TB PCIe 4.0 M.2 SSDs, making it crazier to run them in RAID 0. The card with its cover off is visible below.

Why do we need PCIe 4.0?

Upgrades to PCIe 4.0 are worthwhile, particularly because PCIe 4.0 expansion cards and motherboards are starting to replace PCIe 3.0 as the industry standard.

Better performance from GPUs and other PCIe expansion cards is becoming necessary for more compute-intensive and data-intensive applications, and PCIe Gen 4 meets the needs.

Furthermore, the need for faster and more effective interfaces (pipes) for data transfer is driven by the expansion of the internet, the growing number of IoT devices, and the growing complexity of AI workloads.

PCIe Gen 4 satisfies the requirement by doubling the pipeline width. More bandwidth will be needed in the future to handle the rise in data volume and speed.

Technical developments frequently outpace consumer demand, particularly when it comes to practical applications.

The rate of technological adoption is influenced by the total cost of ownership or TCO.

Even while new technologies have advantages over older ones, the cost of implementing them in the real world can prevent them from being financially feasible.

PCIe 4.0 Bandwidth

Maintaining compatibility with both software and mechanical interfaces, the connection performance bandwidth is double that of the PCIe 3.0 specification, giving 16GT/s.

There is backward compatibility between PCIe 4.0 and previous PCIe versions.

To understand a PCIe Gen 4 device’s maximum bandwidth, one must know how many PCIe lanes it supports.

Because PCIe devices employ “lanes” for data transmission and reception, the more “lanes” a device can use, the more bandwidth it can offer.

A phrase like “x4” for four lanes, “x8” for eight lanes, and so on is usually used to denote a PCIe device’s support for a specific number of lanes.

Processors supporting PCIe 4.0

The following processors support PCIe 4.0 for those wishing to get the highest throughput.

- 11th Gen Core Processors by Intel

- 12th Gen Core Processors by Intel

- 3rd Gen Xeon Scalable Processors by Intel

- Ryzen 3000 and 5000 Series Processors by AMD

- EPYC 7002 and 7003 Series Processors by AMD

Features/Benefits of PCIe 4.0

The primary benefits of PCIe 4.0 are its much faster speed and larger bandwidth, which result in faster data transmission, load times, and improved performance all around. In addition, it features more lanes than PCIe 3.0, which permits the simultaneous connection of more devices without creating a bottleneck.

Increased Bandwidth

PCIe 4.0 can supply up to 16 GT/s of bandwidth, which is a significant increase above its predecessors’ bandwidth.

Faster data transfers as a result shorten the time it takes for huge files, apps, and games to load.

Better Performance for Gaming

Increased bandwidth benefits gamers and professionals doing high-end computer work by improving performance, speeding up loading times, and improving system responsiveness.

Enhanced Data Center Efficiency

PCIe 4.0 increased speed and efficiency translate into greater overall performance for clients’ workloads in data centers, which results in more effective operations and reduced processing delay.

Compatibility with Next-Generation Hardware

By being forward-compatible with upcoming PC and device versions, PCIe 4.0 helps to prevent investments in existing hardware from becoming outdated too soon.

Reduced Power Consumption

PCIe 4.0 devices are made to be more energy-efficient even if they have increased performance. Both consumer electronics and massive data centers benefit from their decreased heat and power consumption.

Understanding of PCIe 5.0

PCIe 5.0 overview

The next iteration of PCIe, known as PCIe 5.0, is a high-speed interface that is commonly used to link parts including Ethernet gear, self-encrypting drives (SEDs), and graphics processing units (GPUs).

For peripheral connections or endpoints, such as graphics cards, SSDs, Wi-Fi, and Ethernet gear, it is the standard motherboard interface.

With maximum data transfer rates of 32 GT/s (giga transfers per second), maximum unidirectional bandwidth of 64 GB/s (gigabytes per second), and maximum bidirectional bandwidth of 128 GB/s, PCIe 5.0 is twice as fast as PCIe 4.0.

What does PCIe 5.0 do?

In comparison to PCIe 4.0 or Gen 4, PCIe 5.0, or Gen 5, is a new PCIe standard that doubles data transmission capacity.

Higher performance on all PCIe peripherals, including SSDs and GPUs, is made possible by this. First, by using fewer lanes, PCIe 5.0 allows system designers to balance bandwidth requirements.

The primary distinction between PCIe 4.0 and PCIe 5.0 that you should be aware of is that PCIe 5.0 provides twice as much total bandwidth as its predecessor.

The bandwidth of a PCIe 5.0 device with 32 lanes is 128GB/s, which is significantly quicker than that of devices that use prior PCIe versions.

To be able to use PCIe 5.0 devices, you may need to upgrade your motherboard, CPU, and even memory.

This can be expensive, as you will need to upgrade these components only to receive support.

Why do we need PCIe 5.0?

PCIe 5.0 will increase operational efficiency for huge public services companies like Google and others that handle massive volumes of data.

Applications in science and engineering will also profit from this expanded bandwidth.

Because PCIe 5.0 has high-speed networking capabilities and can easily manage a 400GbE network connection, it will also play a crucial role in data centers.

PCIe 5.0 Bandwidth

The most recent PCIe standard, PCIe 5.0 (for Peripheral Component Interconnect Express), offers significant bandwidth gains over earlier iterations.

With a maximum theoretical bandwidth of 32 GT/s (giga transfers per second) per lane, Gen5 PCIe was released.

This is equivalent to 64 GB/s for an x16 connection, or about 4 GB/s per lane (both directions).

A single link supporting 3.94 GBps of bandwidth for PCIe 5.0 is also capable of transmitting that 3.94 GBps simultaneously in both directions because the connection standard is duplex.

Processors supporting PCIe 5.0

The processors supported in PCIe 5.0 are,

- Intel’s 12th-generation Core processors (code-named Alder Lake)

- 13th-generation Core processors (code-named Raptor Lake)

- 4th generation Xeon processors support PCIe 5.0.

- AMD’s Ryzen 7000 Desktop Processors and

- Epyc 9004 series also supports PCIe Gen 5.0.

Features/Benefits of PCIe 5.0

The primary advantage of PCIe 5.0 is its much higher data transfer rate, which can dramatically boost high-end computer systems’ performance.

In addition, it provides reduced latency and more bandwidth than PCIe 4.0, making it perfect for data analytics, AI, and machine learning.

The sophisticated features it possesses render it an essential enhancement for high-performance computing settings, augmenting system efficacy.

It also safeguards technological expenditures for the future.

Below are some of the key features of PCIe 5.0:

Increased Data Transfer Speed

In comparison to PCIe 4.0, PCIe 5.0 has twice the data transfer rate, up to 32 GT/s (Giga transfers per second), allowing for quicker performance in applications that require a lot of data.

Enhanced Bandwidth

PCIe 5.0 delivers much more capacity due to its higher data transmission speed, which is advantageous for applications that need high data throughput, like data analytics and high-resolution video editing.

Improved Power Efficiency

PCIe 5.0 is perfect for energy-sensitive operations because it uses more efficient coding and signaling techniques that increase performance and enhance power efficiency.

Greater Scalability

The increased speed and bandwidth enable more scalable solutions, allowing future developments in computing and storage technologies to be accommodated without experiencing bottleneck problems.

Lower Latency

Lower latency and faster application response times are two more benefits of PCIe 5.0 technology developments, especially for real-time processing and gaming applications.

Better Error Correction

More dependable data transport is ensured by enhanced error correction techniques in PCIe 5.0, which is crucial in demanding computing environments and applications.

Backward Compatibility

The backward compatibility of PCIe 5.0 with earlier PCIe device generations ensures a smooth upgrading path and safeguards hardware investments.

Comparison of PCIe 5.0 Vs 4.0

PCIe 5 .0 vs PCIe 4 .0: PCIe has experienced multiple emendations since its inception; currently new motherboards started supporting version 4.0 and version 5.0 supported motherboards are expected to hit the market by 2022.

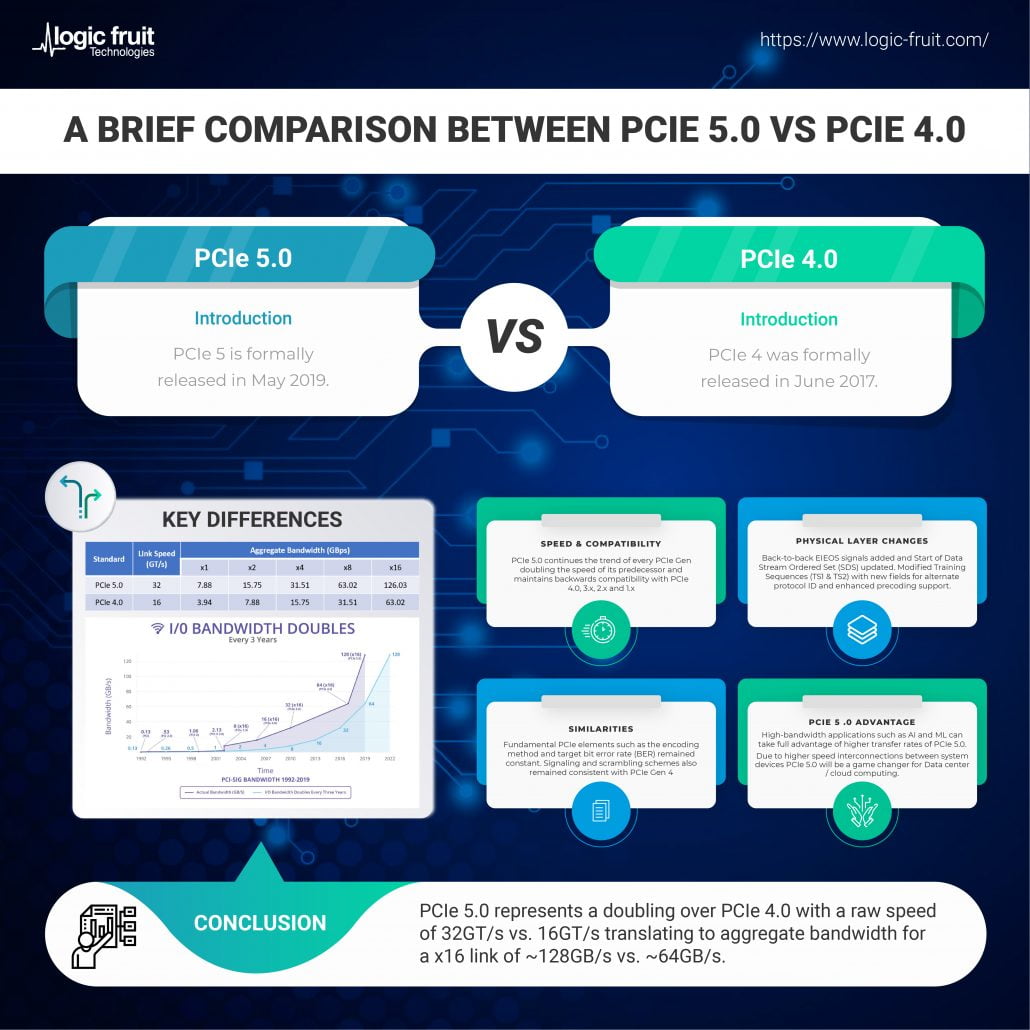

PCIe 4.0 and 5.0 were formally released in 2017 and 2019 respectively. Throughout the entire existence of PCI advancement, this might be the first run through another standard that has been done before the previous had even been dispatched in the consumer market.

The critical feature of any new PCIe version is that it doubles the bandwidth from the previous generation. PCIe 4.0 and 5.0 don’t differ from this behavior and continue the trend along with maintaining the backward compatibility.

Conclusion

In conclusion, what has taken place is a significant step forward in high-speed data transfer with respect to moving from PCIe 4.0 to PCIe 5.0.

In today’s world, where modern applications are becoming more demanding, PCIe 5.0 provides high-speed internet with wider bandwidth necessary for performance improvement on different kinds of machines including gaming devices as well as AI technology among others.

Anyone looking forward to future performance gains then they should consider adopting it such that they can compete favorably with others who have already made this move due to other related reasons.