PCIe’s IDE Encryption and Integrity: Ensuring data security and integrity has become crucial in the quick-paced world of modern computing, where data is the foundation of operations.

The PCI Express (PCIe) bus can be compared to a digital freeway where data travels at breakneck speed. But it has significant risks, just like any busy thoroughfare.

To protect the digital goods traveling over this motorway, PCIe has developed and added an intriguing guardian: the Integrity and Data Encryption (IDE) feature.

As your data rushes through the circuits and connectors of your computer, PCIe IDE acts as a kind of futuristic digital vault to keep it safe.

It protects your private information from prying eyes and ensures that it reaches its destination undamaged.

The PCIe Integrity and Data Encryption feature is redefining data security in the computing industry.

In this thrilling journey, we’ll peel back the layers of this high-tech armor to unveil its secrets. Settle in for an exciting voyage into the PCIe IDE realm, where data security meets cutting-edge technology.

PCIe’s Integrity and Data Encryption Feature (IDE)

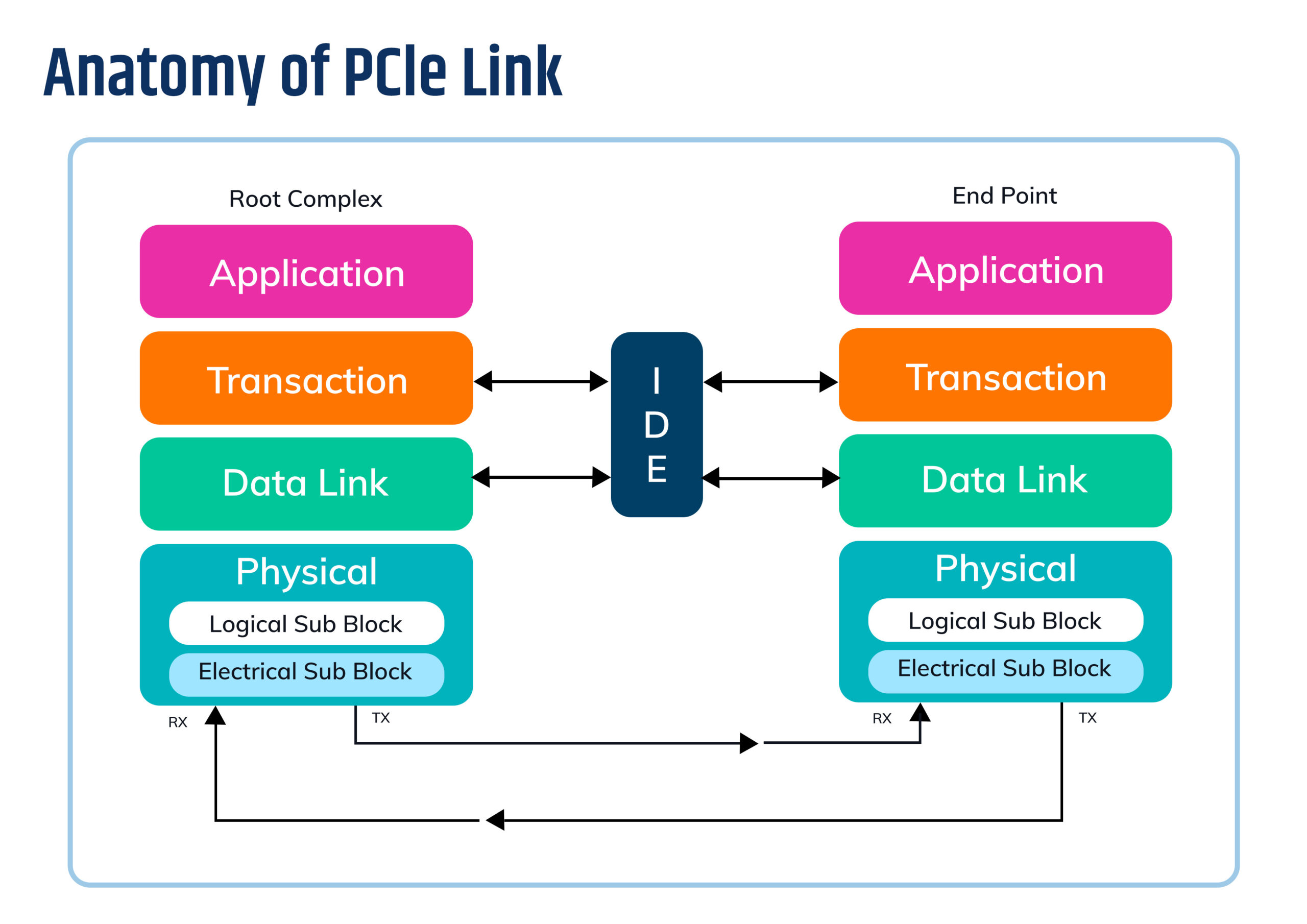

The Integrity and Data Encryption (IDE) tool was developed to secure communication between the various PCIe topology components, including the root complex (RC), switch (SW), and endpoint (EP).

It was introduced by ECN in PCIe (Peripheral Component Interconnect Express) version Gen5.0.

To defend against threats from physical attacks on the link, a new layer called the IDE layer was introduced between the transaction layer and the data link layer.

The IDE layer encrypts data using AES-GCM cryptography, providing data encryption and integrity verification through authentication.

IDE provides encryption at the PCIe link level, ensuring that data between PCIe-connected components like the root complex, switches, and endpoints is secured

The IDE layer is inserted between the transaction and data link layers, ensuring that data remains encrypted through the physical layer over PCIe lanes.

Anatomy of a PCIe Link

A high-performance, all-purpose input/output (I/O) connection called Peripheral Component Connection Express (PCIe®) was created for various computing and communication platforms.

Recent incarnations of the standard use packetized protocol, switch-based technology, point-to-point interconnects, and high-speed serial technology.

Debugging PCIe devices requires capturing and viewing dynamic link behaviors because they strongly rely on link negotiation and training.

To further understand what is happening, let’s dissect the PCIe architecture.

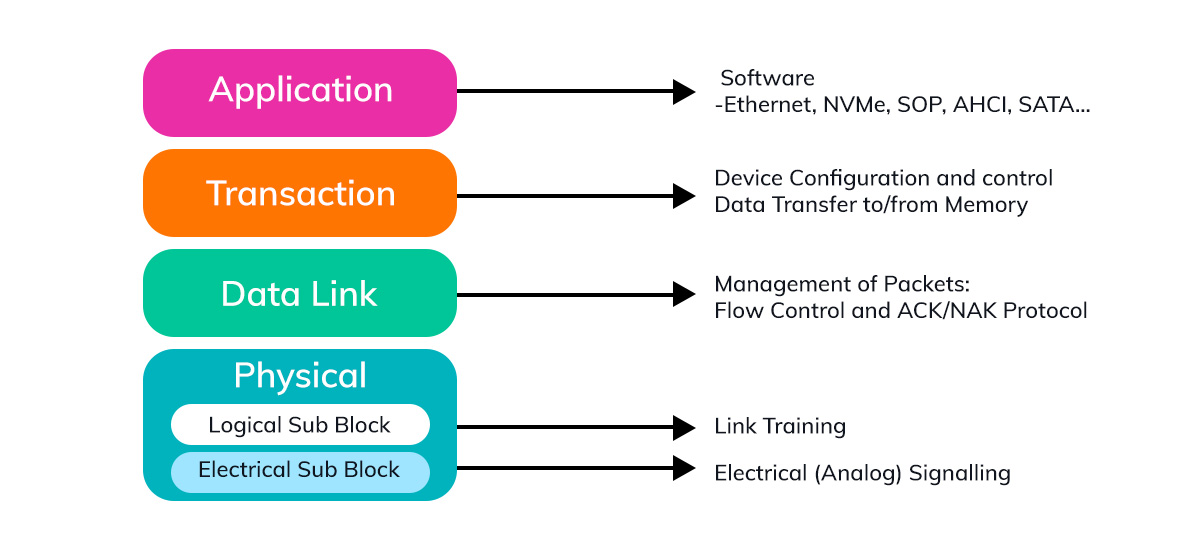

Application Layer

The PCIe specification truly doesn’t address the application layer (or host layer).

The payload is where protocols like Ethernet, Non-Volatile Memory Express (NVMe), and others can be seen. The payload’s content is less important to the PCIe protocol than the way it is transferred across a link.

Transaction Layer

Device configuration for the link is done via the transaction layer. Consider it a way to move memory from the host memory to the device and vice versa.

It provides commands for setting memory reads and writes, which entails setting up the device, enumerating it, and then arranging data transfers between it.

Additionally, it provides systems for reporting messages and errors.

Data Link Layer

The data link layer controls the data flow between those devices. To ensure the integrity of packets traveling over the link, that is where the flow control mechanism and the acknowledgment protocol are located.

Physical layer

The electrical sub-block and the logical sub-block are the two sub-blocks that make up the physical layer at the lowest level.

The analog components necessary for all analog signals are implemented in the electrical sub-block.

State machines are used to create a link in the logical sub-block, which governs how the two devices communicate with one another. To train links with other devices, it generates ordered data patterns, such as training sequences.

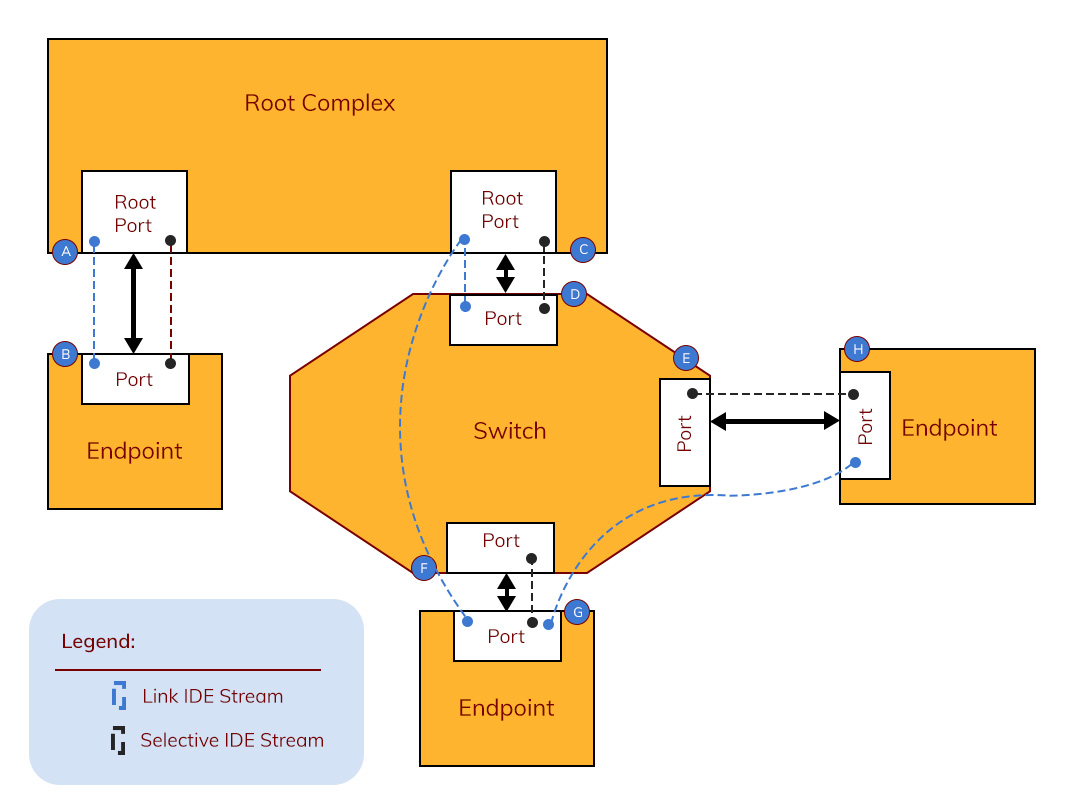

Streams of IDE feature

The Integrity and Data Encryption (IDE) feature provides two distinct types of security streams: the link IDE stream and the selective IDE stream.

The link stream (represented in yellow) secures communication within the PCIe link, ensuring that all data transmitted across the link is encrypted and authenticated. This provides broad protection for all data passing through the link.

The selective stream (represented in blue) is a more targeted security channel between specific devices within the PCIe topology.

This allows for granular control, securing only selected traffic, which can optimize performance while maintaining the necessary data protection.

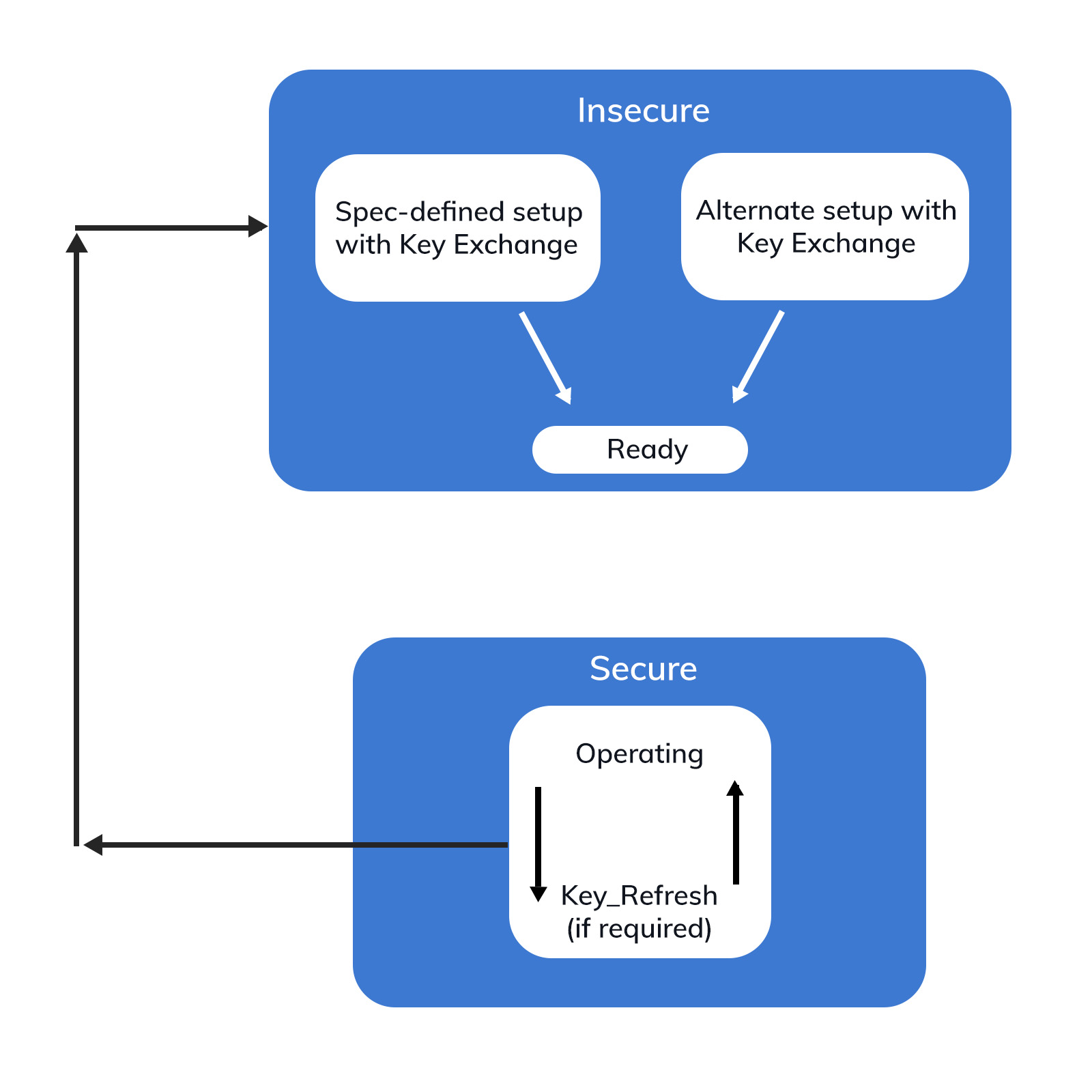

IDE State Machine

A finite state machine (FSM) inside the IDE contains two states: the secure state and the unsecured state. Until it is set up and turned on, the stream is unsecured.

A setup has been established for PCIe gen 6.0. PCIe 6.0 defines a standard setup for securing streams through the IDE mechanism.

The IDE is adaptable for alternative configurations, though. We will concentrate on the PCIe one in this blog.

It is necessary to first construct the stream, set of keys, and INIV configurations before configuring the stream. The stream can be enabled once it has been configured.

If no faults are found or the stream is turned off, the IDE FSM will enter the secure state and remain there.

Setting bit 0 of the link IDE stream control register to a link stream and bit 0 of the selective IDE stream control register to a selective stream both enable the stream.

However, if the stream encounters an issue or is disabled, the FSM reverts to the unsecured state.

To enable the streams:

- Setting bit 0 of the link IDE stream control register activates the link stream.

- Setting bit 0 of the selective IDE stream control register enables the selective stream.

Conclusion

To guarantee the security and dependability of data transfer within PCIe systems, PCIe’s Integrity and Data Encryption Feature (IDE) is a crucial development.

The use of IDE improves the integrity of data transfers, lowering the possibility of manipulation or unwanted access.

Furthermore, it offers strong data encryption tools that support confidentiality and protect sensitive data while it’s being transmitted.

Overall, the addition of IDE considerably improves the security posture of the PCIe architecture, fostering confidence and strengthening the base of contemporary data-driven environments.