JESD204B vs JESD204C IP: The JESD204 interface standard was developed to reduce the number of interconnects required between mixed-signal devices (such as analog-to-digital converters, or ADCs, and digital-to-analog converters, or DACs) and processing units like FPGAs.

JESD204 also provides a standardized mechanism for serializing the digital data from these data converters, thereby improving data transmission efficiency, reducing physical connections, and enhancing overall system performance.

In April 2006, JESD204 became officially available. In the standard, a multi-gigabit serial data link between converter(s) and a receiver, usually a device such as an FPGA or ASIC is detailed.

This edition defined a serial data link as a single serial channel that connects a converter or several converters to a receiver.

A differential pair of interconnects that connect the M number of converters to the receiver via current mode logic (CML) comprises the physical interface, symbolized by the lane.

The link represents the serialized data link between the converter or converters and the recipient.

The frame clock is not only routed to the converter(s) and the receiver, but it also acts as the clock for the JESD204 link between them.

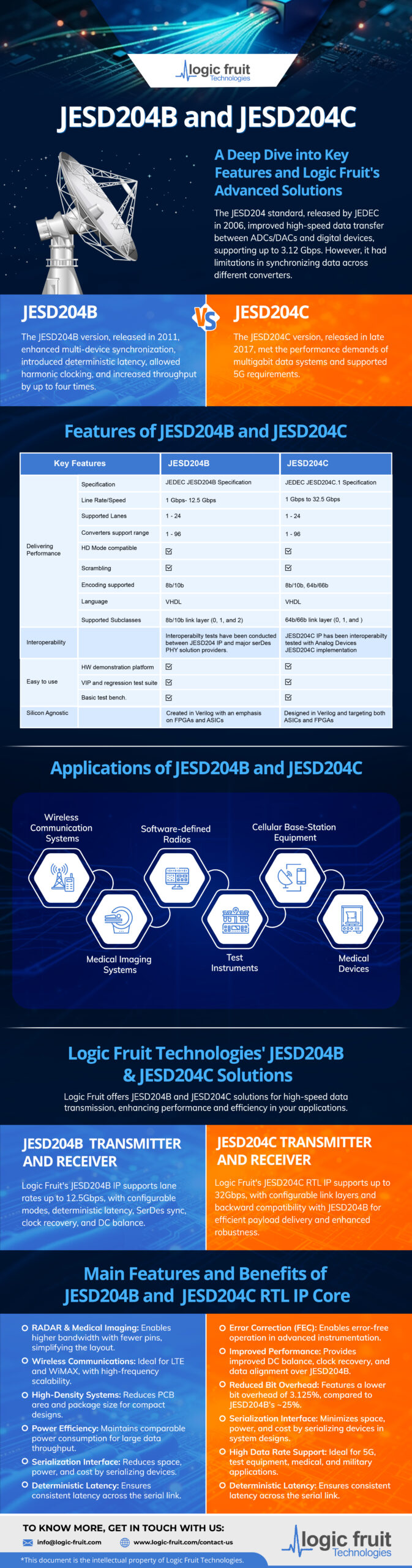

July 2011 marked the release of JESD204B, the standard’s second and most latest iteration. Adding clauses to enable predictable latency was one of the key components of the revised standard.

Additionally, the list of supported data speeds was expanded to include 12.5 Gbps, and descriptions of the different device speed grades were given. Learn more about JESD204B

The Next version of the standard, JESD204C, was published in late 2017 to address the growing performance demands for multigigabit data processing systems of this generation as well as those of the future.

The C iteration of the standard has numerous improvements, many of which increase overall throughput and coding efficiency.

Although JESD204C has various restrictions in subclass-0 operation, it is backward-compatible with the A and B standards. Learn more about JESD204C

The JESD204B and JESD204C, their main characteristics, applications, and Logic Fruit’s JESD solutions are all covered in the infographic below.

JESD204B vs JESD204C

JESD204B and JESD204C Standards with Logic Fruit Solutions

Download Logic Fruit’s JESD204B and JESD204C datasheets to get clear and detailed information about specifications, features, and application guidance.

These datasheets provide the insights needed to integrate and optimize these solutions in your systems effectively.

Logic Fruit’s newly released JESD204D takes data transmission to the next level with blazing-fast speeds and unmatched efficiency.

Built to meet the needs of cutting-edge applications, JESD204D delivers enhanced performance for future-ready systems.