Generations of PCIe:

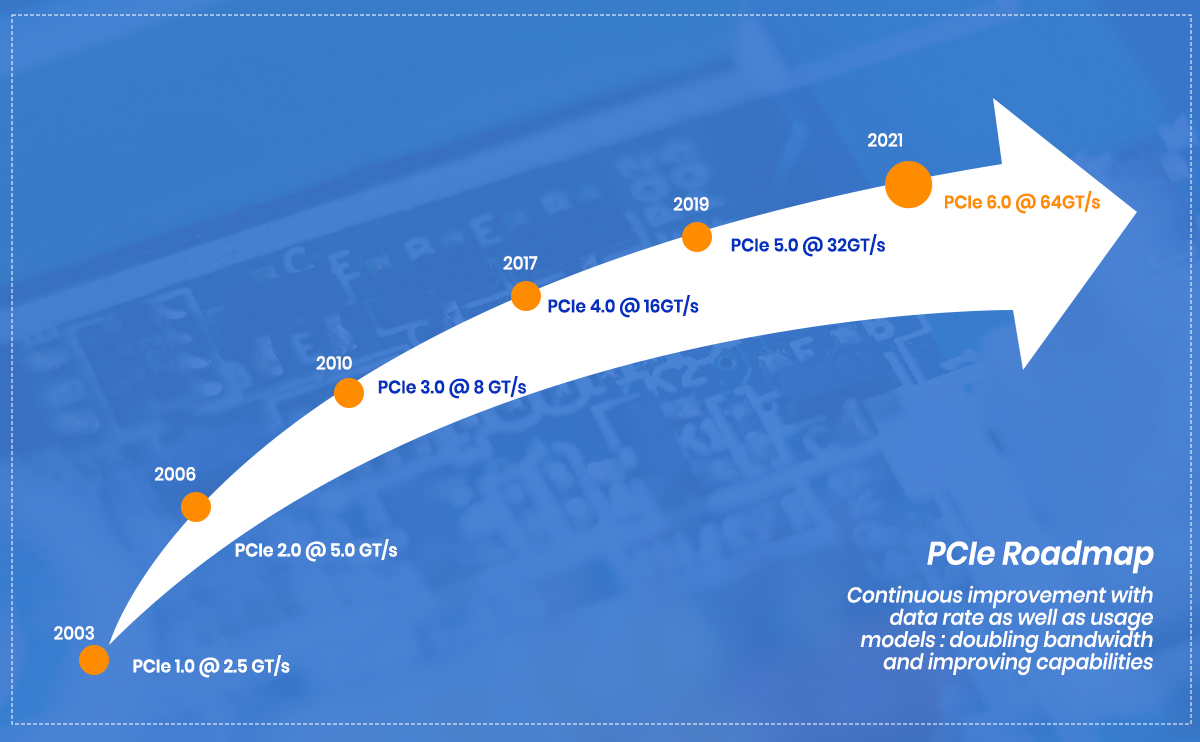

The PCIe 1.0, 2.0, 3.0, and 4.0 versions have contributed significantly to the field of computer architecture and have come to be accepted as industry standards. However, a fresh iteration was required to push the boundaries even further as the demand for quicker and more effective data transport keeps growing. Where PCIe 6.0 enters the picture is in this situation.The most recent revision to the PCIe standard, PCIe 6.0, promises ground-breaking speeds and expanded bandwidth. It is made to meet the rising demands of cutting-edge technology including data centers, high-performance computing, and artificial intelligence. The purpose of PCIe 6.0 is to enable seamless and blazing-fast communication between components, opening up new opportunities and innovation potential. Image Credit

Image CreditIntroduction to PCIe 6.0

PCIe 6.0, also known as PCI Express 6.0, is the latest iteration of the PCI Express (Peripheral Component Interconnect Express) standard.Purpose: PCIe 6.0 is designed to provide significantly higher bandwidth and faster data transfer rates between components in a computer system.Release date: PCIe 6.0 was officially released by the PCI-SIG (Peripheral Component Interconnect Special Interest Group) in 2021.What is PCIe 6.0?

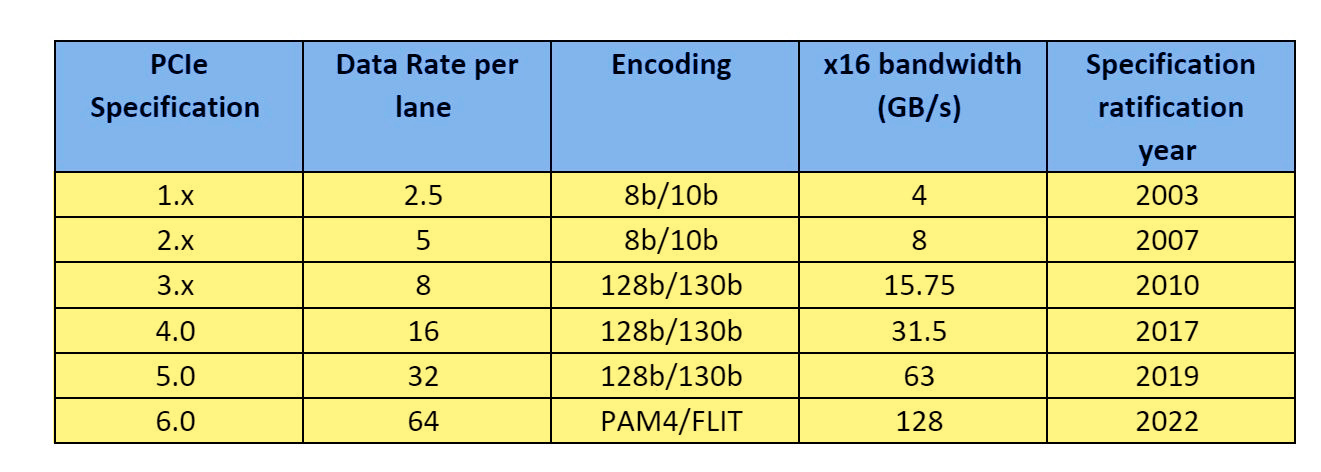

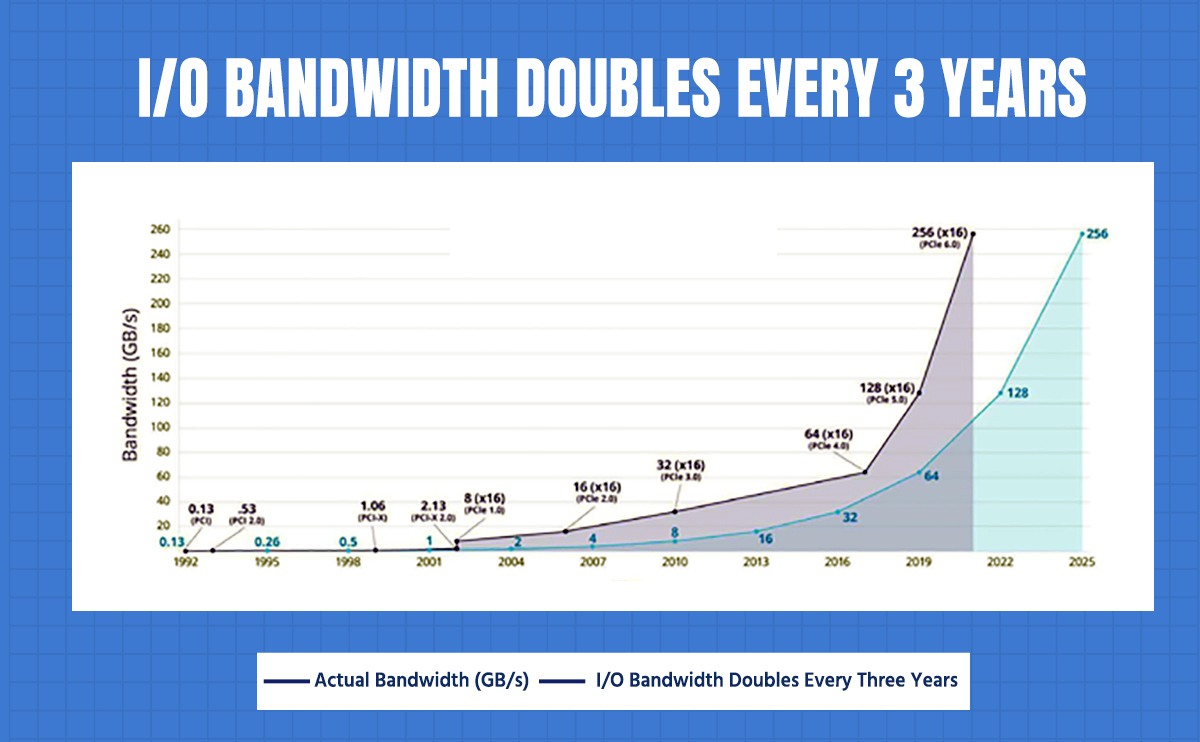

Since PCIe 3, the data rate has doubled with each succeeding iteration of the standard. The data throughput is increased by PCIe 6.0 to 64 Giga transfers per second (GT/s), which is twice as fast as PCIe 5.0. The link’s bandwidth can reach 128 gigabytes per second (GB/s) for an x16 link, typical of graphics and network devices. The PCIe 6.0 link is a full duplex, just like earlier versions, and can transmit 128 GB/s of bandwidth simultaneously in each direction for a total bandwidth capacity of 256 GB/s.Because of its economies of scale, PCIe has spread well beyond servers and PCs. It is appealing for data-centric applications in IoT, automotive, medical, and other fields. The first PCIe 6.0 deployments will focus on applications that need the most bandwidth feasible and are found in the middle of the data center, including AI/ML, HPC, networking, and cloud graphics.The following graph shows how the PCIe specification has evolved. Image Credit

Image CreditKey improvements and enhancements over previous versions:

- Higher data rate: PCIe 6.0 offers a doubling of the data rate compared to its predecessor, PCIe 5.0. It achieves a raw data rate of 64 GT/s (Giga transfers per second) per lane, resulting in a staggering 256 GB/s (gigabytes per second) in an x16 configuration.

- Increased lane count: PCIe 6.0 supports up to 128 lanes, providing greater scalability and flexibility in terms of device connectivity.

- Forward Error Correction (FEC): PCIe 6.0 introduces new FEC mechanisms to enhance error detection and correction, improving data integrity and reliability.

- Backward compatibility: Despite advancements, PCIe 6.0 remains backward compatible with previous generations, allowing seamless integration with existing PCIe devices.

What’s new in PCIe 6.0?

Image CreditTo achieve 64 GT/s, PCIe 6.0 introduces new features and innovations:

Image CreditTo achieve 64 GT/s, PCIe 6.0 introduces new features and innovations:1. PAM4 Signaling:

On the electrical layer, PCIe 6.0 uses PAM4 signaling (“Pulse Amplitude Modulation with four levels”) that combines 2 bits per clock cycle for 4 amplitude levels (00, 01, 10, 11) vs. PCIe 5.0, and earlier generations, which used NRZ modulation with 1 bit per clock cycle and two amplitude levels (0, 1). Image Credit

Image Credit2. Forward Error Correction (FEC)

There are always tradeoffs, and the transition to PAM4 signal encoding introduces a significantly higher Bit Error Rate (BER) vs. NRZ. This prompted the adoption of a Forward Error Correction (FEC) mechanism to mitigate the higher error rate. Fortunately, the PCIe 6.0 FEC is sufficiently lightweight to have minimal impact on latency. It works in conjunction with strong CRC (Cyclic Redundancy Check) to keep Link Retry probability under 5×10-6. This new FEC feature targets an added latency under 2ns.While PAM4 signaling is more susceptible to errors, channel loss is not affected compared to PCIe 5.0 due to the nature of the modulation technique, so the reach of PCIe 6.0 signals on a PCB will be the same as that of PCIe 5.0.3. FLIT Mode:

In FLIT mode, which PCIe 6.0 introduces, packets are structured in Flow Control Units of fixed sizes rather than the variable sizes found in earlier PCIe generations. Since error correction necessitates dealing with fixed-size packets, FLIT mode was initially introduced. However, FLIT Mode also makes data management at the controller level simpler, resulting in improved bandwidth efficiency, lower latency, and a smaller controller footprint. For a moment, let’s talk about bandwidth efficiency: Fixed-size packets eliminate the requirement for packet framing at the physical layer. That translates to a 4-byte save for each packet. Additionally, FLIT encoding eliminates DLLP (Data Link Layer Packets) overhead and 128B/130B encoding from earlier PCIe specifications, leading to much greater TLP (Transaction Layer Packet) efficiency, particularly for large transactions.

In FLIT mode, which PCIe 6.0 introduces, packets are structured in Flow Control Units of fixed sizes rather than the variable sizes found in earlier PCIe generations. Since error correction necessitates dealing with fixed-size packets, FLIT mode was initially introduced. However, FLIT Mode also makes data management at the controller level simpler, resulting in improved bandwidth efficiency, lower latency, and a smaller controller footprint. For a moment, let’s talk about bandwidth efficiency: Fixed-size packets eliminate the requirement for packet framing at the physical layer. That translates to a 4-byte save for each packet. Additionally, FLIT encoding eliminates DLLP (Data Link Layer Packets) overhead and 128B/130B encoding from earlier PCIe specifications, leading to much greater TLP (Transaction Layer Packet) efficiency, particularly for large transactions.PCIe 6.0 encoding

Every 8 bits of data were converted into 10-bit characters before being delivered in PCIe versions 1.0 and 2.0, which results in a 20% overhead (you must transfer 10 bits of data even though you’re only attempting to send 8). To communicate those same 2 extra bits, PCIe 3.0, 4.0, and 5.0 all employ 128b/130b encoding, which reduces the overhead to just 1.5%.According to the PCI-SIG, PCIe 6.0 employs 1-bit to 1-bit (1b/1b) encoding, so the data encoded has no overhead. This means that if you want to send 8 bits over PCIe Gen 6, you only need to send 8 bits. However, there is still some overhead in the form of additional FEC/CRC packets.

Every 8 bits of data were converted into 10-bit characters before being delivered in PCIe versions 1.0 and 2.0, which results in a 20% overhead (you must transfer 10 bits of data even though you’re only attempting to send 8). To communicate those same 2 extra bits, PCIe 3.0, 4.0, and 5.0 all employ 128b/130b encoding, which reduces the overhead to just 1.5%.According to the PCI-SIG, PCIe 6.0 employs 1-bit to 1-bit (1b/1b) encoding, so the data encoded has no overhead. This means that if you want to send 8 bits over PCIe Gen 6, you only need to send 8 bits. However, there is still some overhead in the form of additional FEC/CRC packets.PCIe 6.0 vs. PCIe 5.0: Performance and Features

In this section, we will compare the performance and features of PCIe 6.0 with its predecessor, PCIe 5.0. Both of these standards represent significant advancements in high-speed data transfer, but there are notable differences between them. Let’s explore the critical aspects of PCIe 6.0 and how it compares to PCIe 5.0.Data Rate and Bandwidth:

- PCIe 5.0: PCIe 5.0 introduced a doubling of the data rate compared to PCIe 4.0, reaching a speed of 32 GT/s (Gigabytes transfers per second) per lane. This translates to approximately 4 GB/s (gigabytes per second) of raw bandwidth per lane.

- PCIe 6.0: PCIe 6.0 takes another leap in performance, doubling the data rate of PCIe 5.0. It offers a stunning speed of 64 GT/s per lane, providing approximately 8 GB/s of raw bandwidth per lane.

Lane configurations:

- PCIe 5.0: PCIe 5.0 maintains the same lane configurations as its predecessor, supporting x1, x2, x4, x8, x16, and x32 configurations.

- PCIe 6.0: PCIe 6.0 also supports the same lane configurations as PCIe 5.0, allowing for x1, x2, x4, x8, x16, and x32 configurations.

Encoding and signaling:

- PCIe 5.0: PCIe 5.0 introduced PAM4 (Pulse Amplitude Modulation 4-level) encoding, which enables more data to be transmitted per clock cycle compared to the previous NRZ (Non-Return-to-Zero) encoding used in PCIe 4.0.

- PCIe 6.0: PCIe 6.0 continues to use PAM4 encoding, but with additional enhancements to improve signal integrity and reduce errors, enabling reliable data transmission at higher speeds.

Forward Error Correction (FEC):

- PCIe 5.0: PCIe 5.0 introduced Reed-Solomon FEC (Forward Error Correction), which helps detect and correct transmission errors, improving the reliability of data transfer.

- PCIe 6.0: PCIe 6.0 enhances the FEC mechanism by adopting a more efficient low-density parity check (LDPC) FEC algorithm. LDPC provides superior error correction capabilities while reducing latency compared to Reed-Solomon FEC.

Power Efficiency:

- PCIe 5.0: PCIe 5.0 introduced power-saving features, including L1 sub-states and L1.2 idle power management, which help reduce power consumption when the link is idle or operating at lower speeds.

- PCIe 6.0: PCIe 6.0 further enhances power efficiency by introducing new power management capabilities, allowing for deeper power-saving states and better overall energy efficiency.

Backward compatibility:

- PCIe 5.0: PCIe 5.0 is backward compatible with PCIe 4.0, meaning PCIe 5.0 devices can be used in PCIe 4.0 slots, albeit at reduced speeds.

- PCIe 6.0: PCIe 6.0 is expected to maintain backward compatibility with previous versions, allowing PCIe 6.0 devices to work with older PCIe slots, albeit at lower speeds.

Conclusion:

In comparison to its predecessor, PCIe 5.0, PCIe 6.0 provides outstanding performance enhancements and cutting-edge capabilities. It is the next significant advancement in high-speed data transport.

For demanding applications including high-performance computing, data centers, AI, ML, and storage systems, PCIe 6.0 offers quicker and more efficient data processing capabilities with a two-fold increase in data throughput and enhanced bandwidth.

Data transmission reliability and energy economy are further increased with the introduction of PCIe 6.0 thanks to improvements in encoding, error correction, and power efficiency.

Large datasets, demanding workloads, and the processing needs of future technologies may all be handled without issue thanks to these developments.

While upgrading to PCIe 6.0 has many advantages, it’s necessary to take into account how well the existing infrastructure will work with the new standard and whether suitable hardware is readily available.

Since PCIe 6.0 is a relatively new standard, it might take some time before it is widely used while the market gets used to this most recent development.

Future PCIe standards promise to be quicker and more effective in terms of data transport. We should expect PCIe to advance further as technology develops, opening the door to improved connectivity and performance in the always-expanding digital environment.

In summary, PCIe 6.0 sets a new standard for high-speed data transfer, offering unparalleled performance, improved features, and increased efficiency. Its capabilities make it a compelling choice for industries that demand high-bandwidth solutions, propelling innovation and enabling the next generation of computing experiences.

About Logic Fruit Technologies

Logic Fruit Technologies is a leading provider of custom engineering solutions for high-performance embedded computing. With expertise in PCIe technology, we offer a range of services including product development, testing and validation, and hardware design for various industries including automotive, aerospace, and medical devices.

Logic Fruit Technologies delivers customized solutions for high-performance embedded computing using PCIe technology. Our services include product development, testing, validation, and hardware design for various industries.

Logic Fruit Technologies has also been a member of PCI-SIG since 2017. As a member of PCI-SIG, Logic Fruit can collaborate with tier-1 semiconductor companies to develop effective design-to-test methodologies and decrease test costs for these advanced devices.